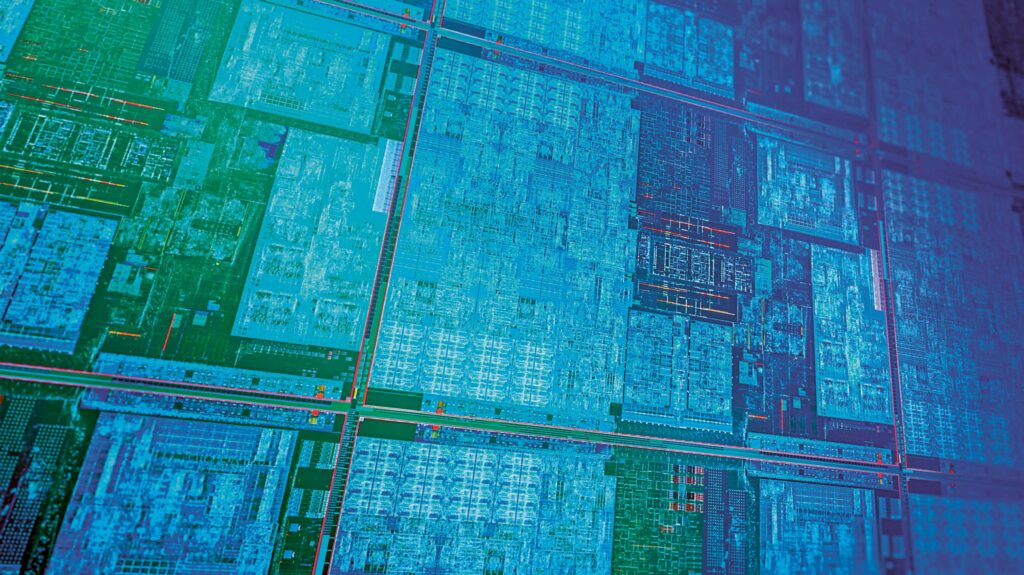

Durante décadas, los transistores de los circuitos integrados han ido reduciendo su tamaño, lo que ha dado lugar a chips cada vez más potentes. En este artículo, Porsche Engineering relata cómo los investigadores y la industria trabajan para mejorar unos chips que, en un futuro, acabarán beneficiando a la industria del automóvil.

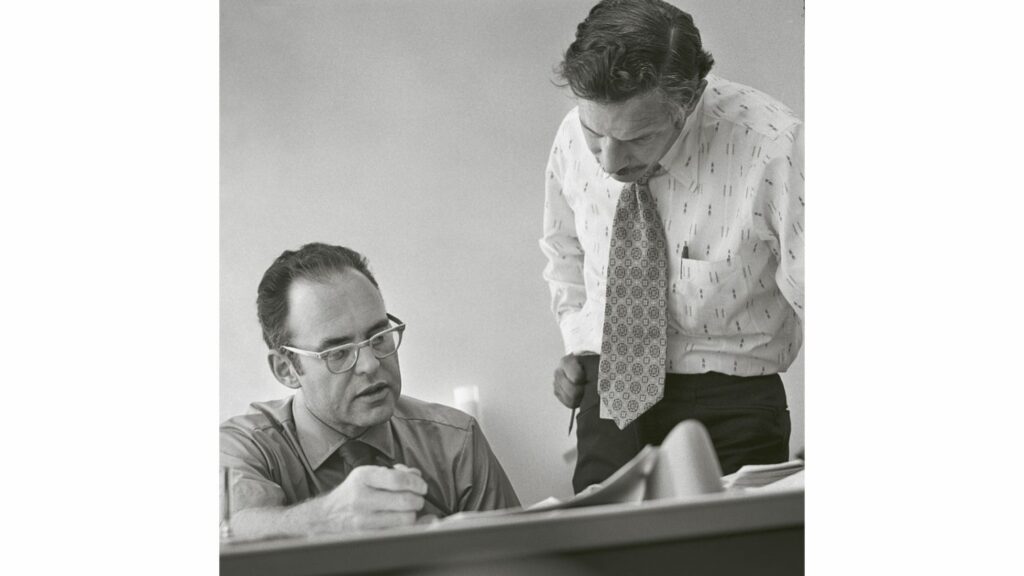

El origen de la electrónica moderna tuvo lugar el 16 de diciembre de 1947 en Bell Labs, Nueva Jersey (EE. UU.). Fue entonces cuando el físico Walter Brattain logró por primera vez amplificar un voltaje eléctrico con un componente semiconductor improvisado. Había nacido el transistor. Por primera vez, existía una alternativa a los voluminosos y poco fiables tubos de vacío que, además, consumían mucha energía. Desde el punto de vista de la apariencia, aquel ingenio de Brattain, que constaba de una placa de germanio, un triángulo de plástico, una lámina de oro y un clip, tenía muy poco en común con los chips modernos, pero presagiaba la era de los ordenadores personales, los teléfonos inteligentes y los coches con funciones automatizadas de conducción.

El nuevo componente electrónico podría usarse como amplificador y como interruptor y, junto con otros elementos como resistencias y capacitores, podría convertirse en un circuito integrado (IC) en una sola placa semiconductora. En las décadas siguientes, las empresas de semiconductores consiguieron hacer que los componentes fueran cada vez más pequeños para así poder colocar un número cada vez mayor de ellos en la misma superficie. Ya en 1965, Gordon Moore fue capaz de ver que el número de transistores por unidad de área aumentaría exponencialmente.

El escalado simple alcanza sus límites

La predicción de Moore ha demostrado ser correcta durante décadas. Pero ahora finalmente está llegando a sus límites, porque la reducción gradual en el tamaño de los MOSFET (Transistor Semiconductor de Óxido de Metal de Efecto de Campo, por sus siglas en inglés) como interruptores en los chips ya no existe: “Hace unos 15 años, la gente se dio cuenta de que el escalado simple había llegado a su fin”, asegura la investigadora Heike Riel, miembro de IBM en el Centro de Investigación de la empresa en Rüschlikon, Suiza. “Es por eso que los fabricantes reemplazaron por primera vez el dióxido de silicio como material aislante en los transistores con los llamados materiales High-K, manteniendo la misma geometría MOSFET. Esto hizo posible producir chips con estructuras de 45 nm de tamaño”.

Pero este truco solo podría mantener viva la Ley de Moore durante unos años más. Por esta razón, los fabricantes de chips comenzaron a utilizar una nueva arquitectura de transistores para componentes aún más pequeños en la primera mitad de la década de 2010: el FinFET, en el que el canal conductor entre el terminal fuente y los terminales drenadores tiene forma de aleta y está encerrado en varios lados por el terminal puerta. “Esto hace que sea mucho más fácil controlar el flujo de corriente en el transistor”, dice Riel. “Se utilizaron FinFET a partir de 22 nm de tamaño de estructura y ahora son comunes en circuitos integrados”.

El FET más evolucionado

Pero el denominado FinFET tiene ya un sucesor. Comenzando con tamaños de estructura de cinco nanómetros, el GAAFET es hoy el futuro. “El GAAFET, el canal conductor entre los terminales fuente y drenadores consta de varios nanocables de silicio paralelos, cada uno de los cuales está completamente encerrado por la puerta”, explica Riel. “Esta es la geometría óptima para controlar el flujo de corriente. También ahorra espacio en los chips porque varias de estas estructuras de nanocables, que forman el canal del transistor, se superponen entre sí”. El mundo del automóvil también se beneficiará de desarrollos como la arquitectura GAAFET en el futuro, porque tanto las nuevas y potentes Plataformas de Computación de Alto Rendimiento (HCP) como las sucesoras de las muchas unidades de control descentralizadas y los procesadores especiales para conducción autónoma, dependen de chips con alta potencia de cálculo. Sin embargo, ni siquiera GAAFET podrá salvar la Ley de Moore a largo plazo: más allá de un tamaño de estructura de tres nm, las cosas se pondrán difíciles. Este límite podría alcanzarse en tres o cuatro años.

“De este modo, está llegando a su fin una fase ingeniosa de mejora”, dice el profesor Thomas Schimmel, Director de Nanotecnología del Instituto Tecnológico de Karlsruhe (KIT). “Hasta ahora, siempre se había encontrado una solución técnica que permitía una mayor miniaturización del transistor clásico, pero ahora se han alcanzado dimensiones atómicas en los chips. Gracias al efecto túnel de la mecánica cuántica, los electrones pueden atravesar aisladores, lo que inutilizaría los componentes. Esto se debe a que, contrariamente a las ideas de la física clásica, los electrones pueden superar las barreras incluso cuando en realidad no tienen suficiente energía para hacerlo”. La introducción selectiva de átomos extraños en el silicio de alta pureza durante el proceso de producción, un procedimiento conocido como “dopaje”, ya no funciona de manera confiable con estructuras cada vez más pequeñas.

No hay un sucesor claro a la vista

Por eso se busca un sucesor del transistor que aumente aún más el rendimiento de los circuitos electrónicos en el futuro. La investigadora de IBM Heike Riel enumera toda una serie de alternativas al MOSFET, como el transistor de efecto de campo de nanotubos de carbono (CNFET) y el FET de túnel (TFET). En el CNFET, la corriente fluye a través de diminutos tubos de carbono. Este año, investigadores del MIT han demostrado que estos interruptores rápidos y energéticamente eficientes pueden producirse en fábricas de chips convencionales. Los TFET tienen un diseño similar al de los transistores convencionales, pero aprovechan el efecto túnel mecánico cuántico para la conmutación. Ahorran energía y son rápidos. Es incierto si la carrera la ganará el CNFET, el TFET o cualquier otro enfoque. “Actualmente se está investigando mucho, pero no hay un claro favorito para suceder al MOSFET optimizado de silicio”, comenta Riel.

Schimmel, investigador del KIT, apuesta a largo plazo por el transistor monoatómico: en este transistor, un electrodo de control desplaza un átomo que puede cerrar el diminuto hueco entre dos terminales y permitir así el flujo de corriente. “En principio, funciona como un relé con dos estados estables”, dice Schimmel que, en 2004, desarrolló junto a su equipo el primer transistor de átomo único. “Esto hace que el transistor monoatómico no solo sea un interruptor, sino también una memoria no volátil. También podría sustituir a los chips RAM convencionales como memoria principal en los ordenadores. Como conserva su estado incluso sin energía, los ordenadores ya no tendrían que reiniciarse en el futuro, sino que podrían seguir trabajando inmediatamente después de una pausa”.

Otra ventaja es que el transistor de un átomo requiere un voltaje mucho menor que el MOSFET y, por tanto, solo consumiría una diezmilésima parte de la energía por operación de conmutación. Esto resolvería el problema del calor en los chips actuales y se podría alcanzar una frecuencia de reloj de hasta 100 giga hercios. Schimmel ya ha construido un primer CI con dos de sus novedosos transistores y, para una posterior producción en serie, se podría utilizar una combinación de procesos ya empleados en la industria de semiconductores y procedimientos galvánicos. “Es como galvanizar la carrocería de un coche, solo que a escala atómica”, dice el científico de Karlsruhe.

Nuevas arquitecturas de chips y ordenadores

Como alternativa a la miniaturización cada vez mayor de los componentes, también son posibles nuevos enfoques de la arquitectura de los chips. Por ejemplo, ir hacia una tercera dimensión: para acumular más potencia en los circuitos, apilar varias capas como ya se hace hoy en las memorias flash. En el futuro, los fabricantes también podrían aplicar una capa de semiconductores compuestos, como el arseniuro de indio y galio (InGaAs), a otra de transistores convencionales de silicio.

Son adecuados para tareas especiales como la amplificación especialmente rápida, para la emisión o detección de luz y también como posibles componentes cuánticos. Muchos expertos apuestan por la integración de estas funciones adicionales en los chips para compensar la desaparición de la Ley de Moore. Adoptan un nuevo enfoque: en lugar de “más Moore” (mayor miniaturización), prefieren “más que Moore” (la combinación de funciones digitales y no digitales en el mismo chip).

La computación en memoria

La computación en memoria, que pretende eliminar en los ordenadores comunes la separación espacial entre la unidad de cálculo y la memoria, promete una potencia de cálculo y una eficiencia energética mucho mayores. Esto eliminaría el transporte de bytes entre el microprocesador y la memoria RAM, que consume mucho tiempo y energía. Por ejemplo, los cálculos vectoriales-matriciales de una red neuronal pueden realizarse mediante una arquitectura de conmutador de barras cruzadas analógica en lugar de digital. En este enfoque, se cruzan dos haces de líneas horizontales y verticales, cada uno de los cuales actúa como entrada y salida de la red neuronal. En sus puntos de intersección, las líneas están conectadas entre sí mediante elementos de memoria no volátil que representan los factores de corrección (el “conocimiento”) de la red neuronal. Los valores de entrada de esa red se aplican como valores de tensión analógica a las líneas horizontales. Los resultados de los cálculos están disponibles casi instantáneamente en las líneas verticales, también en forma analógica, y sin ningún transporte de datos.

Las memorias no volátiles en los puntos de cruce de las líneas incluyen memristores, novedosos componentes electrónicos cuya resistencia puede modificarse permanentemente mediante una tensión aplicada externamente. Se pueden fabricar con los procesos existentes en la industria de semiconductores. Los memristores pueden utilizarse para realizar cálculos en redes neuronales entre diez y cien veces más rápido, dependiendo de la aplicación, y su eficiencia energética también puede mejorarse entre diez y mil veces. Los vehículos autónomos, para los que las redes neuronales serán muy importantes, también se podrían beneficiar de estas mejoras de rendimiento y eficiencia. El ejemplo demuestra que, aunque la Ley de Moore llegue pronto a sus límites, el aumento continuo del rendimiento de la electrónica está lejos de terminar.

MOSFET, FinFET y GAAFET

Durante décadas, el MOSFET (izquierda) ha sido el interruptor principal de la tecnología digital y ha mantenido la Ley de Moore gracias a su continua miniaturización. El voltaje entre el electrodo de la puerta y el de la fuente determina la corriente que fluye por el canal desde la fuente hasta el drenador. En el FinFET (centro), el canal tiene forma de aleta para que la puerta pueda rodearlo por tres lados. Esto mejora el control del flujo de corriente en comparación con el MOSFET, donde la puerta solo puede actuar sobre el canal desde arriba. En el GAAFET (derecha), la puerta rodea completamente el canal de nanocables de silicio. Esta es la geometría óptima para controlar el flujo de corriente.

Alternativas futuras al diseño convencional de transistores

En el TFET (izquierda), a diferencia del MOSFET, la fuente y el drenador están “dopados” de forma diferente. Utiliza el efecto túnel mecánico cuántico: el voltaje entre la puerta y la fuente determina si los portadores de carga pueden hacer un “túnel” a través de la barrera energética entre la fuente y el drenador y si es posible un flujo de corriente. En el CNFET (centro), el canal entre la fuente y el drenador está formado por nanotubos de carbono. También en este caso, la tensión puerta-fuente determina el flujo de corriente. En el transistor de un átomo (derecha), la tensión entre la fuente y la puerta desplaza un solo átomo, que cierra o abre el circuito entre la fuente y el drenador (posición verde/roja).

Ley de Moore

Hace 55 años, Gordon Moore hizo una notable predicción en la revista Electronics: el entonces director de investigación de Fairchild Semiconductor y posteriormente cofundador de Intel, afirmó en 1965 que el número de transistores por chip se duplicaría cada año. Por tanto, ya en 1975 sería posible alojar unos 65.000 en una diminuta oblea de silicio. La “Ley de Moore” se ha ido retocando continuamente a lo largo de los años, pero ha demostrado ser esencialmente correcta y se ha convertido en la pauta para los fabricantes de semiconductores. Hasta hoy, han conseguido duplicar el número de transistores por unidad de superficie en intervalos cortos. Sin embargo, en el futuro esto ya no será posible. Entonces habrá que conseguir un mayor rendimiento de los chips por otros medios.

En resumen

Es probable que la nueva miniaturización del transistor MOSFET y sus variantes FinFET y GAAFET alcance sus límites en los próximos años. Para que los chips sean cada vez más potentes en el futuro, los investigadores y la industria trabajan en nuevos diseños de transistores, como los FET de túnel, y en nuevas arquitecturas, como la computación en memoria.